Internship

Amazon AI Applied Science Intern

In collaboration with Prof. Aviral Kumar · Accepted at ICLR’26 · Paper ↗

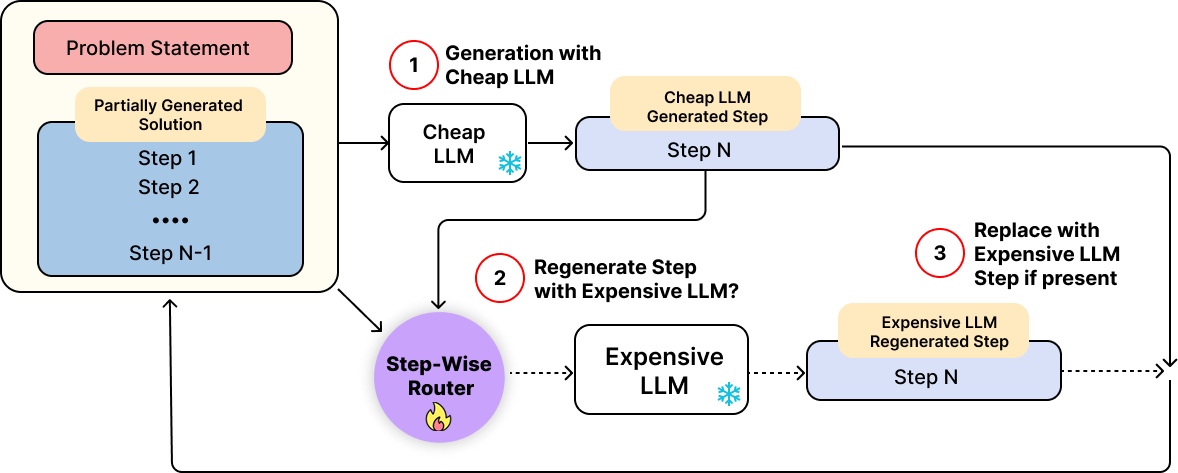

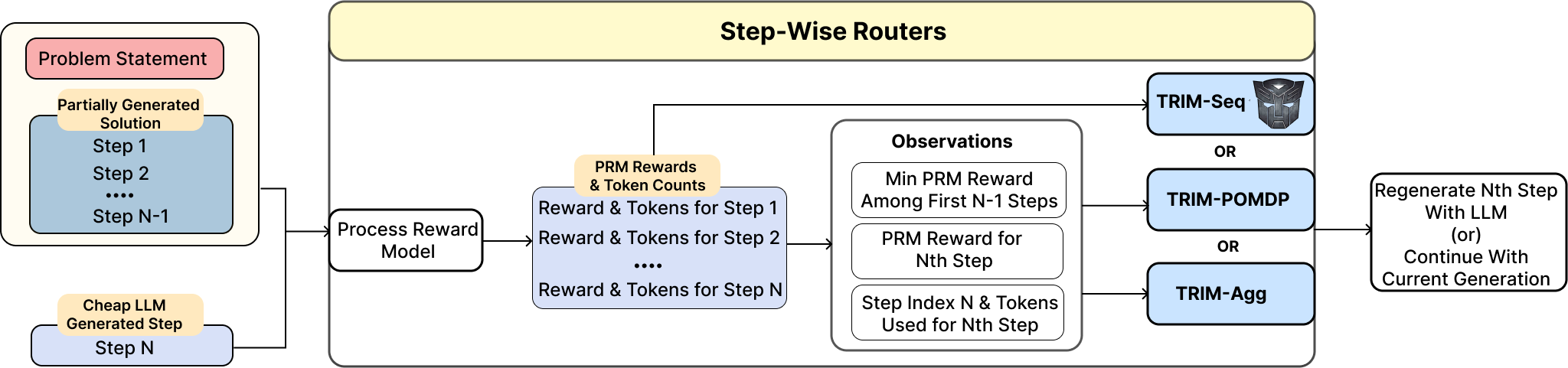

During the summer of 2025, as an Applied Science intern at Amazon AI, I worked on dynamic LLM routing for multi-step reasoning tasks in collaboration with Prof. Aviral Kumar. In this work, we introduced an approach for targeted, stepwise routing that escalates only critical steps to stronger, more expensive LLMs, intervening precisely where the partial reasoning trace risks diverging from a correct solution. Our key insight is that targeted step-level interventions can fundamentally improve inference efficiency by limiting expensive calls to those steps where stronger models prevent cascading errors.

We further developed RL-trained and POMDP-based routing policies that demonstrated up to 5× higher cost efficiency over contemporary routing approaches on the AIME and MATH-500 benchmarks, while maintaining the accuracy of the strong expensive model with 75% fewer tokens drawn from it (with the remaining tokens generated by a cheaper, weaker LLM). This work introduces a principled alternative to one-shot query routing by treating routing as a sequential decision problem.

Google Silicon Engineering Intern

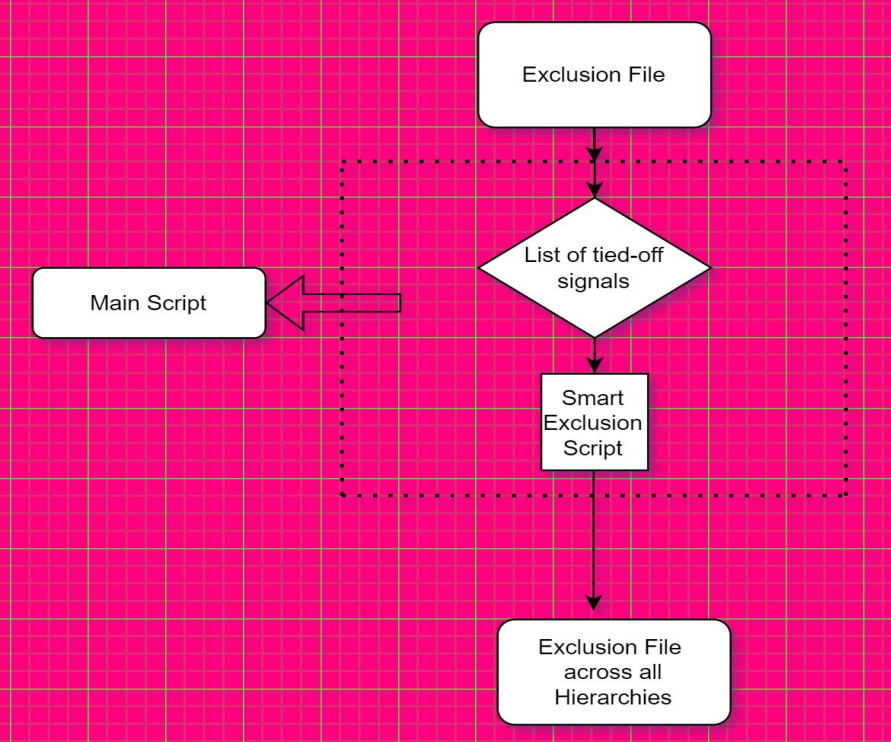

During the summer of 2023, I interned at Google as a Silicon Hardware intern, where I worked on four significant projects over 10 weeks. In my first project, I conducted toggle coverage analysis using Python-based flows to generate exclusion files aimed at optimizing design verification. These exclusion files captured tied-off or floating signals within the Device Under Test (DUT) and were used to exclude them during verification, streamlining the overall design verification process.

Additionally, I implemented the Smart Exclusion feature, automating the generation of exclusion files across all hierarchies using the design elaboration database. This further optimized verification by significantly reducing the time required to exclude connected signals across multiple hierarchies.

In a subsequent project, I implemented automated checkers for retaining flops during teardown and low-power mode operation. This involved generating a comprehensive list of internal flops declared across multiple SystemVerilog files, integrating it into the existing change list, running test cases, and troubleshooting errors. For my final project, I developed a script to automate the parameter verification flow, enabling detection of parameter-value mismatches in RTL files and reporting errors when mismatches occurred.